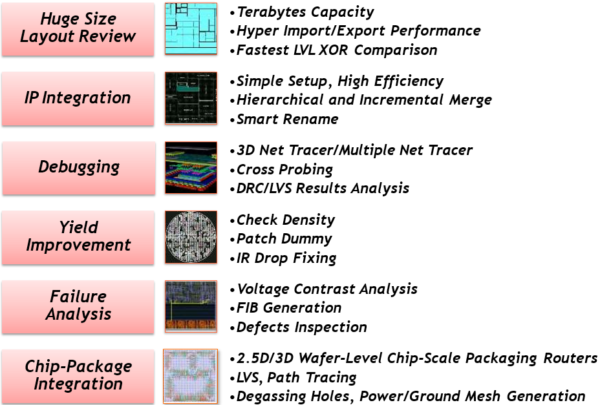

OVERVIEW

Today’s semiconductor industry faces the dynamic nature in either SOC or SIP path-finding and diversity of applications in IoT, automotive, mobile, high-performance computing and even heterogeneous components integration. For example, a top-level layout assembly task normally manages hundreds of sub-blocks in either a SOC GPU chip, or an advanced-node testchip design, or a multi-chip SIP project; while each sub-block owner may have many design re-spins. The high-performance layout integration platform is highly desired to embrace the common challenges in chip-scale, wafer-/panel-level layout integration of complicated design intents, post ECO &dummy engineering, revisions and huge data size and/or with multiple database formats.

THUNDER is a versatile layout integration platform to support heavy layout handling efforts from post P&R, IP merge automation &management, physical ECO verification (XOR LVL, connectivity, etc), DRC/LVS debugging interface, and even (in-line inspection) defect-to-layout mapping, failure analysis and chip-package integration (interposer vs. InFO RDL-routing, pins connectivity, etc). ThunderDB is the proprietary database and is efficient to handle huge layout data with the extreme performance of up to 600+GB GDS equivalent per minute. Users can then perform big data analysis for further processing (e.g. 3D-view, cross-section, density mapping, wafer map), machine-learning based optimization, and manipulating data from GDS, OASIS, LEF/DEF, MEBES, OpenAccess and 3rdparty tools output.

HIGHLIGHTS

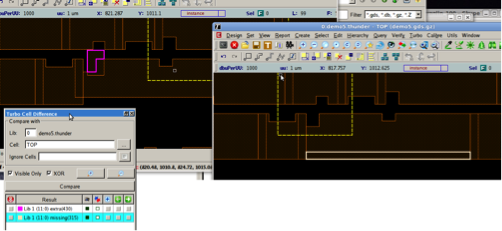

FASTEST LVL COMPARISON

THUNDER provides the fastest LVL comparison, scalable to data size, with GUI visualization to quickly identify the delta among two designs. Customer benchmarking shows that THUNDER LVL consumes minimal runtime memory, even on the industry’s biggest chips.(Fig-1)

Fig-1. Interactive Layout Comparison

IP MERGE AUTOMATION

THUNDER provides system integration for IP from GDS/LEF/DEF files with great flexibility such as standard cell replacement, don’t-change list, etc. It performs layout comparison during renaming, which eliminates unnecessary renaming. It supports hierarchical IP merge with incremental change. It generates a summary of missing cells, renamed cells, identical cells, and cross-reference.

BOOLEAN OPERATION

THUNDER provides intuitive multiple-Boolean expression to generate shapes on original design directly.

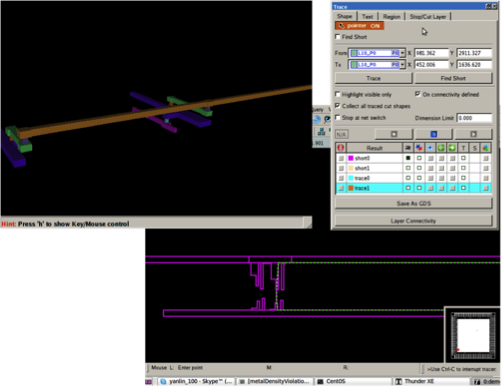

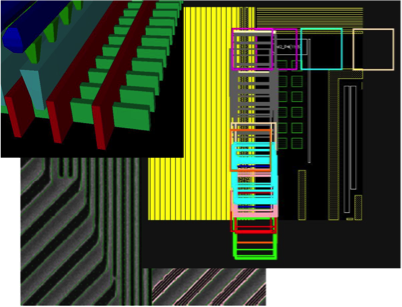

PHYSICAL NET TRACER/FAST TRACE/MULTIPLE TRACER

THUNDER powerful net tracer provides both tracing, multiple tracing and finding “shorts”, with net highlighting and 3D display visualization. It supports both location-based and pin text-based tracing, and even grouping layers connectivity (identity layers: multi-pattern layers, dummy layers). Other debugging functions such as stop layer, net switching detection, and power/ground short detection. (Fig-2)

Fig-2. Physical Net Tracer &Short Locator

Fig-2. Physical Net Tracer &Short Locator

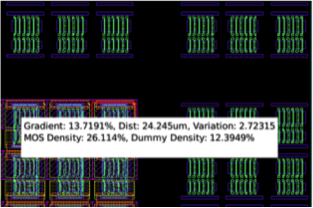

DENSITY MAP GENERATION &CHECKING

THUNDER provides the fastest interactive density mapping generation and violation checking with GUI visualization. It provides density variation checking, which is critical for advanced technology nodes. (Fig-3)

Fig-3. Interactive Density Checking

Fig-3. Interactive Density Checking

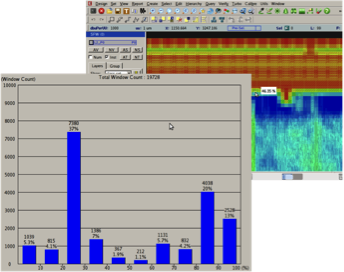

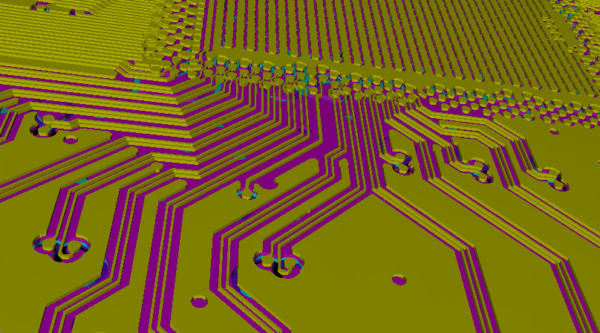

FAILURE ANALYSIS

THUNDER provides a series of functionality to assist the tedious defect inspection job, such as KLA-scanned results viewing, image overlay and extraction, pattern grouping and matching, voltage contrast analysis, FinFET 3D view, cross-section, etc. (Fig-4)

Fig-4. Failure Analysis Related Functionality

Fig-4. Failure Analysis Related Functionality

HIGHLIGHT MISSING VIAS ON POWER/GROUND NETS

To mitigate the IR-drop issues, THUNDER can perform a quick analysis of power/ground nets to highlight areas with missing vias and fix them by inserting vias. (Fig-5)

Fig-5. Fix Missing Vias

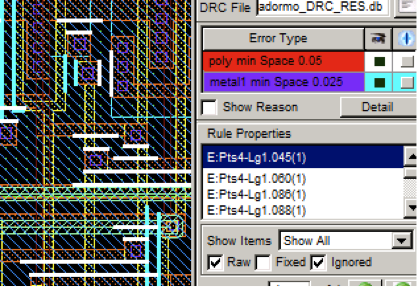

HUGE CAPACITY DRC/LVS/DEFECT EXPLORER

THUNDER provides seamless integration with 3rdparty layout verification and wafer inspection tools. It helps the user to navigate and debug a huge number of DRC/LVS errors and defects efficiently (handles 2+TB DRC results). It also supports Calibre short isolation result with 3D display and cross probing. (Fig-6)

Fig-6. DRC Result Viewer

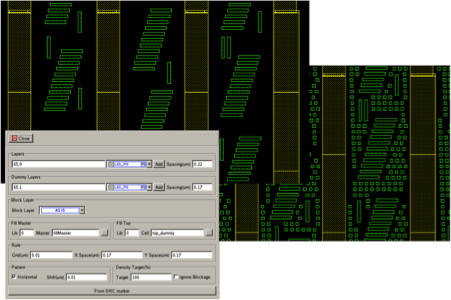

DUMMY FILL PATCHING

THUNDER can fill dummy patterns to low-density area interactively with the target percentage. It creates vertical/horizontal patterns with offset. It can also take Calibre DRC marker as the target area. (Fig-7)

Fig-7. Interactive Dummy Fill Patching

Fig-7. Interactive Dummy Fill Patching

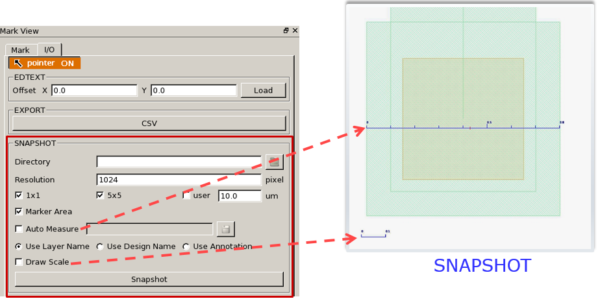

MARK VIEW

THUNDER provides a “SNAPSHOT” feature and supports taking jpg images based on Mark View points as center with user-specified dimension. The “Auto Measure” option adds a ruler of the shortest distance on the image. In addition, a Multi-Thread feature is added to better perform large quantity images. (Fig-8)

Fig-8. Snapshot

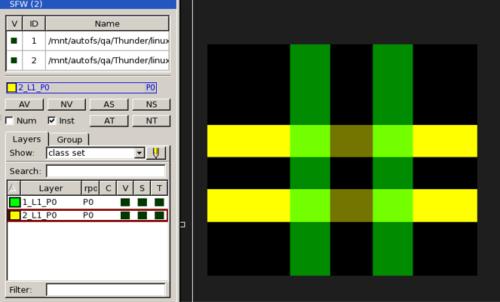

LAYERS OVERLAY

THUNDER provides users to overlay several selected GDS/OASIS files and shows the overlap area with a different color. (Fig-9)

Fig-9. Layers Overlay

SiP INTEGRATION

THUNDER provides the industry’s first integrated router for SiP. It provides a unified routing framework to handle from Fanout RDL, Interposer to Substrate. It also provides a rich set of functions for chip-package integration such as power distribution network, shielding, degassing hole, wire-bond planning, connectivity checking and design rule checking. (Fig-10)

Fig-10. SiP Integration

POWERFUL SCRIPTING

THUNDER supports db-level API in Perl/Tcl/ Python with a built-in debugger.

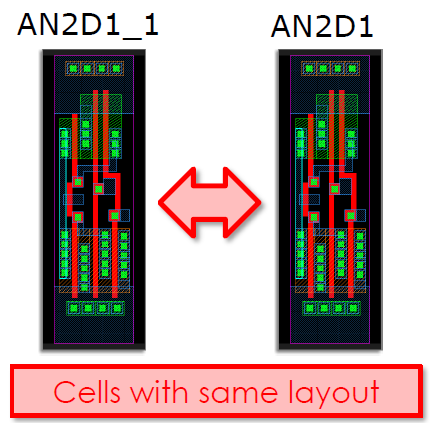

LIB CONSOLIDATION

THUNDER can consolidate duplicated layouts to reduce the file size. (Fig-11)

Fig-11. Cells Comparison

CACHE BROWSER

THUNDER provides a friendly GUI to manage cache files.

THUNDER DEFECT DRC

THUNDER helps the foundry users to investigate the root cause of the defect much more efficiently.